本文介绍IC设计中最常见的六种设计规则检查(DRC)错误类型,以及Siemens EDA旗下的Calibre nmDRC工具如何帮助设计师快速发现、分析和解决这些问题,确保流片成功。

设计规则检查:成败的关键时刻

每位集成电路设计师都会经历同样紧张的时刻:流片前的最后一次设计规则检查。

- 通过:版图将被送往制造

- 失败:需要数天甚至数周的返工,延误项目进度并消耗资源

设计规则检查(DRC)是连接设计意图和可制造硅片之间的最后一道关口。它验证版图中的每一层是否遵循代工厂定义的几何和连接约束——这些规则是经过多年工艺表征精心制定的。

但真相是,并非所有DRC运行都生而平等。结果的准确性完全取决于规则文件背后的引擎。这就是为什么Calibre nmDRC仍然是准确、高性能物理验证的可信基础。

让我们探讨六种频繁出现的DRC错误类型,以及Calibre nmDRC如何为设计师提供可视性、精度和控制能力,在最终签核之前就解决这些问题。

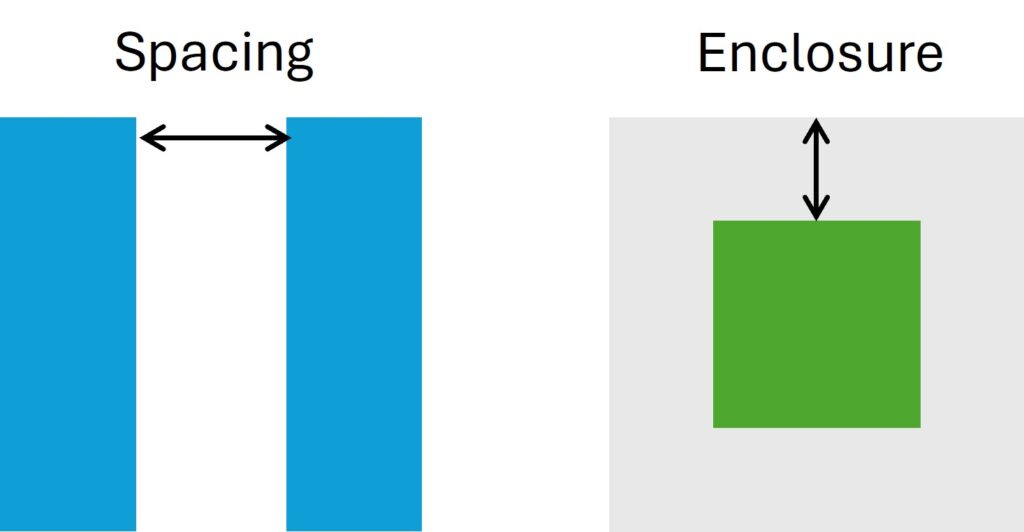

1. 金属间距和包围违例

问题描述

在纳米尺度下,即使最小的几何偏差也可能导致重大的良率问题。间距和包围违例发生在以下情况:

- 两个形状放置得过于接近

- 一层(例如接触孔)未被另一层(如金属层)充分包围

这些检查听起来简单,但实际上很快就会变得复杂。先进的规则通常依赖于局部上下文,包括:

- 宽度相关的间距规则

- 多层交互

- 甚至应力或拓扑效应

Calibre nmDRC如何帮助

- 纳米级精度几何引擎:即使在高度弯曲或非曼哈顿布局中,也能精确测量距离和重叠

- 层次化验证:确保间距检查高效扩展,无论设计包含多少重复单元

- 规则驱动与基于方程的方法结合:捕获确定性和条件性间距行为,不遗漏任何问题

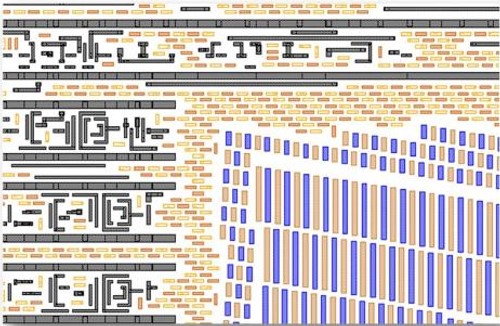

2. 密度和填充错误

问题描述

化学机械抛光(CMP)工艺要求每层表面密度保持一致。不均匀的图案密度可能导致:

- 过度或不足抛光

- 金属凹陷

- 介质层腐蚀

Calibre nmDRC如何帮助

- 集成密度窗口检查:量化版图中的金属覆盖率,确保符合代工厂阈值

- Calibre YieldEnhancer with SmartFill:自动插入基于模型的填充图案以实现均匀性,并调用Calibre nmDRC确保填充不会影响时序或违反其他间距规则

- SmartFill回注:将数据回注到LEF/DEF、OpenAccess、OASIS和GDSII,确保下游提取和仿真准确反映最终填充后的版图

对于复杂的SoC,SmartFill和nmDRC作为单一生态系统运作——分析密度、插入填充并在一个连续流程中验证结果。

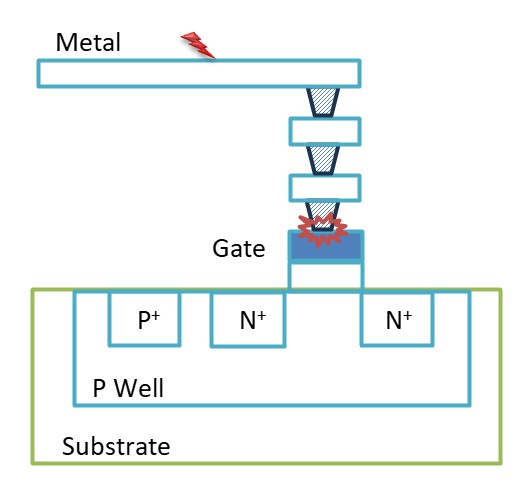

3. 天线效应

问题描述

随着晶体管缩小,薄栅氧化层越来越容易受到制造过程中等离子体充电的影响。长互连线可能会积累电荷并释放到栅极,永久性损坏器件。

Calibre nmDRC如何帮助

- 专用天线规则检查:根据工艺规则精确计算金属对栅极的面积比,检查制造过程中可能因金属线感应电荷导致的晶体管失效

- eqDRC属性过滤:提供数值反馈,突出显示超过阈值的网络。eqDRC是SVRF(标准验证规则格式)的一项操作

- 注释错误标记:在Calibre RVE中直接引导设计师到问题网络,无论是在定制还是自动化设计工具中

这些检查对高压、模拟或射频布局至关重要,在这些设计中,天线敏感性因网络而异。通过Calibre nmDRC,工程师可以自信地测量、可视化和纠正天线风险。

4. 过孔和接触孔错位

问题描述

连接金属层的每个过孔都代表一个潜在的故障点。即使轻微的错位或不充分的包围也可能造成:

- 高阻抗接触

- 开路缺陷

这些缺陷在硅片制造后几乎无法修复。

Calibre nmDRC如何帮助

- 直接数据库访问:允许DRC引擎读取原生版图格式(Milkyway、LEF/DEF、OpenAccess、OASIS、GDSII)而无需转换,保持层精度

- 层次化检查:重用重复过孔结构的数据,减少运行时间而不牺牲准确性

Calibre nmDRC的精度确保每个过孔都满足代工厂的几何和套刻要求,即使在密集的互连堆叠中也是如此。

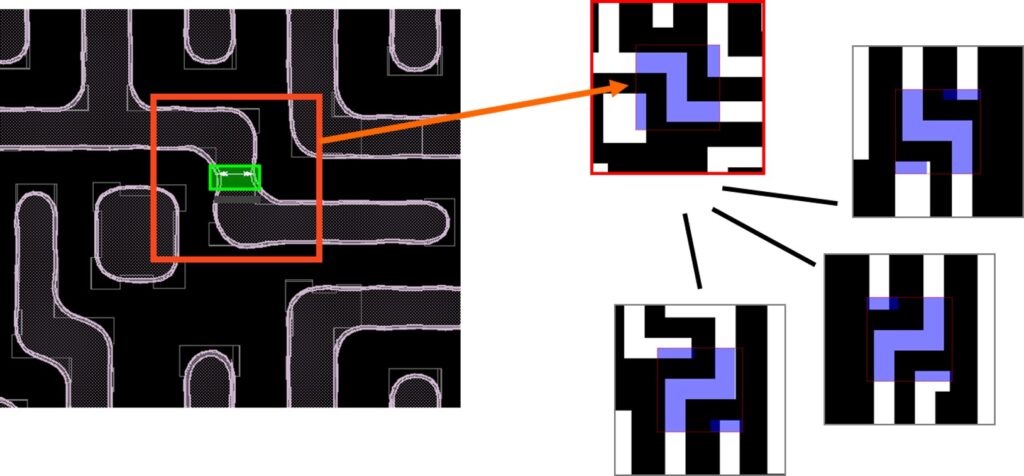

5. 基于图案的热点

问题描述

某些限制良率的问题根本无法通过规则语句轻易捕获。它们源于特定的几何配置,例如:

- 线端桥接

- 缺口角

- 在光刻过程中相互作用不良的复杂多层图案

Calibre nmDRC如何帮助

- 图案匹配技术:直接内置于nmDRC引擎中,在用于传统DRC的同一规则文件中搜索已知的问题形状

- 代工厂图案库支持:代工厂通常在其签核规则文件中包含这些图案库,为设计师提供与工艺认证期间使用的相同预测洞察

- 多重曝光和光学网格检查:进一步扩展28nm以下节点的覆盖范围,涵盖光刻驱动的约束

通过将图案分析直接集成到规则检查中,Calibre nmDRC实现了单一统一流程,涵盖标准和上下文敏感的几何形状。

6. 高压检查

问题描述

高压检查对于具有显著电压差的设计至关重要,例如电源管理单元。在这些设计中,标准的几何间距不够充分。高压检查确保:

- 相邻金属线根据电位差具有足够的间隙

- 防止电击穿、电弧和可靠性问题

Calibre nmDRC如何帮助

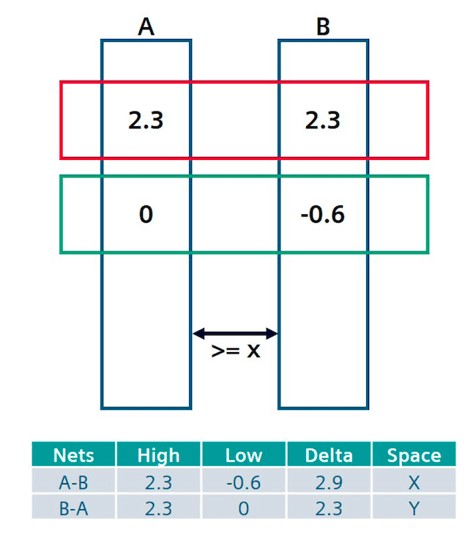

- 电压感知规则应用与DFM DV:Calibre nmDRC利用其可制造性设计(DFM)设计验证(DV)能力,根据相邻网络之间的电压差动态应用间距规则。这超越了静态几何检查,实现了智能的电气感知验证

- 集成网络属性分析:它无缝集成网表信息(包括电压分配)与物理版图数据。这使Calibre nmDRC能够精确计算电位差并应用相应的高压间距要求

- 全面的击穿预防:代工厂可以在Calibre nmDRC中定义复杂的高压规则集,使设计师能够验证其版图是否满足严格的电气隔离要求,防止昂贵的现场故障并确保产品安全

通过Calibre nmDRC,设计师可以自信地应对高压集成的复杂性,确保其设计能够抵御电击穿并满足关键的可靠性标准。

不仅是发现错误:更快地修复它们

发现违例只是工作的一半——真正的价值在于能够多快地理解和纠正它。Calibre nmDRC包含先进的调试和报告功能,旨在大幅缩短这个循环。

关键生产力特性

- Calibre Vision AI:强大的调试环境,使用AI识别系统性问题并尽早解决最有影响的错误

- Calibre RVE:提供错误标记与版图形状之间的交互式交叉探测

- 可定制的HTML批处理报告:让工程师预筛选、排序和过滤错误,专注于关键类别

- 用户定义属性分组:工程师可以按用户定义的属性对结果进行分组,嵌入快照,甚至使用色图或直方图来说明违例分布

- 自动豁免管理:从后续运行中删除预先批准的例外,保持报告清晰且可追溯

这些功能使物理验证审查周期更快、更直观、更协作——对于大型分布式设计团队来说这是一个重要优势。

Shift-left DRC:更早发现问题

等待完整的 sign-off 运行才发现数千个错误已不再实用。为了压缩验证周期,设计团队正在将DRC提前到版图流程的早期阶段——这种方法称为shift-left verification。

Calibre nmDRC Recon

Calibre nmDRC Recon使这种转变成为现实:

- 使用部分规则子集执行有针对性的早期阶段DRC运行

- 在设计师编辑版图时提供即时反馈

- 使用与签核DRC相同的Calibre规则语法和几何引擎,结果完美关联

这消除了流程末端的冗余调试。

早期DRC可见性意味着:

- 更少的后期意外

- 更快的收敛

- 版图和验证团队之间更好的协作

为什么代工厂和设计师信任Calibre nmDRC

上面讨论的每项检查——间距、密度、天线、过孔和图案分析——都依赖于设计与制造之间的一致关联性。这种一致性之所以存在,是因为代工厂在Calibre nmDRC中构建其规则文件。

核心优势

- 被绝大多数主要代工厂使用:用于工艺开发和验证

- 提供全面、准确且经过验证的签核物理验证:涵盖所有技术节点

- 快速、可扩展的运行时间:从单CPU到企业计算网格

- 支持主要设计格式的直接数据库访问:无需数据转换

- 提供增强的DRC调试:以最高准确性更快获得结果

简而言之,定义规则的工具与验证版图的工具是同一个——在工艺开发和设计实现之间形成闭环。

持续创新的文化

随着设计几何的演进,Siemens EDA的Calibre团队不断扩展平台,引入新方法:

- 光学网格和间距检查

- 基于方程的分析

- 基于模型的填充

- 3D IC验证

这种承诺确保工具始终领先于新兴的工艺挑战,为下一代节点做好准备。

创新历程

- 当行业转向多重曝光时,Calibre nmDRC已经具备分解分析功能

- 当设计师需要更快的比较时,Calibre Fast XOR使版图对版图检查几乎瞬间完成

- 随着DRC调试变得更加数据密集,可定制的HTML报告和数据库级可视化为复杂的错误分析带来了清晰度和速度

这种稳定的创新步伐,以及与整个半导体生态系统的深度合作,使Calibre nmDRC始终与现代IC设计的需求保持一致。

结论:首次流片成功的DRC标准

设计规则检查仍然是设计可制造性的最基本衡量标准。但在规则复杂性爆炸和工艺窗口缩小的时代,信任DRC结果与通过它们一样重要。

通过结合以下优势:

- 代工厂认证的准确性

- 高级规则特性化

- 层次化可扩展性

- 无与伦比的调试可见性

Calibre nmDRC使工程师能够以最高效率从违例发现走向解决。

它不仅仅是一个DRC工具——它是连接设计、制造和创新的验证标准。

当设计在整个设计阶段保持Calibre-clean时,它才是真正的签核就绪。

相关资源:

参考链接: